在嵌入式系统设计中,实时时钟(RTC)模块是维持精确计时和日历功能的核心。然而,面对像EPSON RTC-72421A这样的经典芯片,其引脚功能与时序逻辑的复杂性常常让工程师感到困惑。如何正确理解CS、ALE、IRQ等关键信号?如何根据数据手册设计出稳定可靠的读写时序?本文将为您提供一份**解决方案导向**的深度指南,从引脚定义出发,逐步拆解其时序逻辑,助您彻底掌握RTC-72421A的设计精髓,避免常见的通信与中断陷阱。

RTC-72421A核心引脚功能详解

深入理解每个引脚的角色是成功应用RTC-72421A的第一步。其引脚配置直接决定了芯片与微处理器的交互方式,是系统稳定运行的物理基础。

电源与时钟引脚:系统稳定运行的基石

VCC和VSS是芯片的主电源引脚,通常连接+5V和GND。VDD和VSS2则用于连接备用电源,例如纽扣电池,以确保在主电源断开时,时钟计时和内部RAM数据不丢失。X1和X2引脚外接32.768kHz的晶体振荡器,为芯片提供精准的时基。确保电源纯净、晶体负载电容匹配准确,是获得稳定计时的首要条件。

总线控制引脚(CS, ALE, RD, WR):与微处理器的沟通桥梁

这组引脚定义了芯片的并行接口模式。CS(Chip Select)是芯片使能信号,低电平有效。ALE(Address Latch Enable)用于锁存地址。RD(Read)和WR(Write)则分别控制数据的读取和写入操作。这四者协同工作,构成了标准的Intel总线接口时序,使得该芯片能够无缝对接如8051系列等众多经典微控制器。

关键信号时序逻辑深度剖析

仅仅理解引脚定义是不够的,精确的时序配合才是通信成功的关键。数据手册中的时序图是设计的金科玉律。

芯片选择(CS)信号的双重角色与模式切换时序

CS信号不仅用于使能芯片,还参与工作模式的切换。当CS从高电平变为低电平时,芯片进入活跃的读写模式。需要特别注意CS的建时间和保持时间要求。在切换操作间隙,如果CS被拉高一段时间,芯片可能会进入低功耗的待机模式。因此,在连续操作时,应确保CS保持稳定的低电平,除非有意切换模式。

地址锁存使能(ALE)与读写(RD/WR)时序配合详解

一个完整的写操作时序通常如下:首先,微处理器将目标地址置于数据/地址总线上,然后产生一个ALE正脉冲,其上升沿将总线上的地址锁存至RTC内部。接着,微处理器将待写入的数据置于总线上,最后产生一个WR负脉冲,将数据写入指定的寄存器。读操作时序类似,区别在于在RD负脉冲期间,RTC将数据驱动到总线上。必须严格遵守数据手册中关于ALE、RD、WR脉冲宽度的最小时间要求。

中断(IRQ)系统配置与应用指南

IRQ引脚是RTC-72421A实现事件通知的关键输出,有效利用它可以避免主处理器频繁轮询,节省系统资源。

IRQ引脚功能与中断标志寄存器解析

IRQ是一个开漏输出引脚,低电平有效,需要外接上拉电阻。其触发条件由内部多个中断标志寄存器控制,主要包括周期中断(如每秒、每分)和闹钟中断。工程师需要通过写操作配置相应的控制寄存器,来使能特定的中断源。例如,设置“周期中断使能位”和“中断标志位”的逻辑关系,决定了IRQ信号的输出行为。

如何配置周期中断与闹钟中断的实用步骤

配置一个周期中断通常遵循以下步骤:首先,向周期中断频率选择寄存器写入代码,设定中断周期(如1秒)。然后,向中断标志控制寄存器写入,将对应的中断标志位清零(如果需要),并设置中断使能位为有效。最后,确保全局中断控制位已打开。当预定时间到达时,芯片会置位中断标志,并将IRQ引脚拉低。主处理器响应中断后,必须通过读操作清除中断标志,才能使IRQ引脚恢复高电平,为下一次中断做好准备。

常见设计陷阱与调试排查清单

即使理解了原理,实际设计中仍可能遇到问题。以下清单有助于快速定位故障。

通信失败:从电源、时钟到CS信号的排查路径

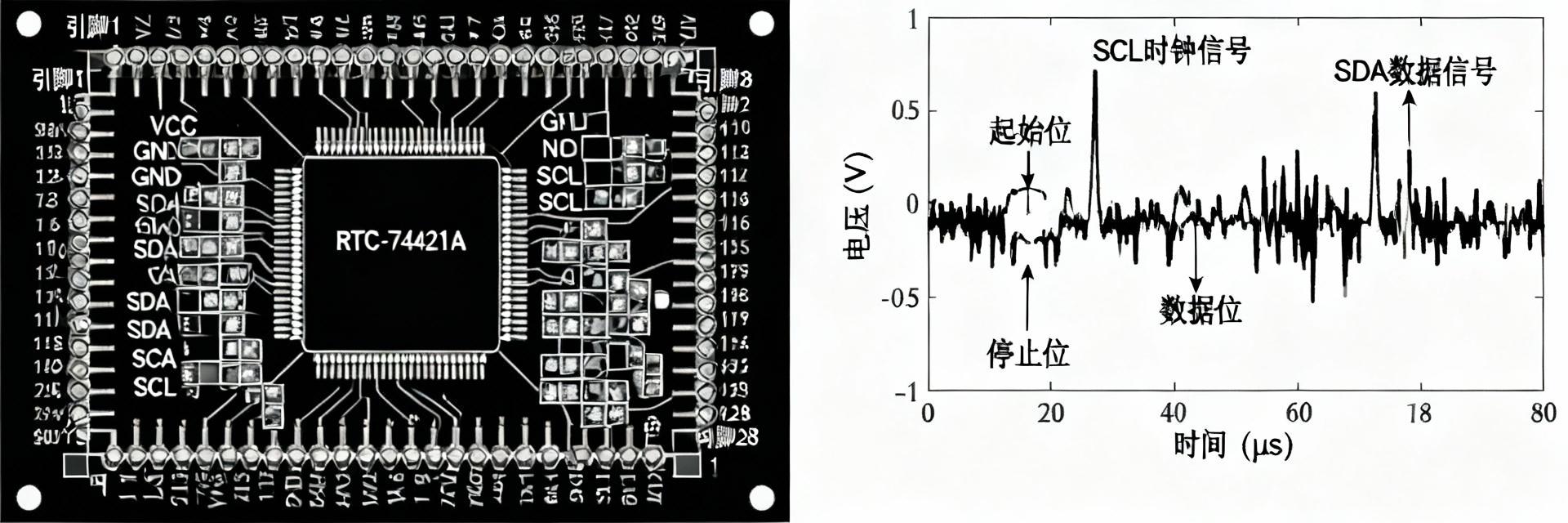

若无法读写寄存器,请按顺序检查:1. **电源**:测量VCC和备用电源电压是否在额定范围(如4.5V至5.5V)内且稳定。2. **时钟**:用示波器检查X1引脚是否有32.768kHz的正弦波,幅度是否足够。3. **控制信号**:用逻辑分析仪或示波器捕获CS、ALE、RD/WR的时序,对照数据手册检查脉冲宽度、建和保持时间是否满足要求。4. **上拉电阻**:检查数据总线和IRQ引脚是否已正确连接上拉电阻。

中断不触发:寄存器配置与IRQ引脚电平的检查清单

如果IRQ始终无输出,请检查:1. **寄存器配置**:确认已正确写入中断使能寄存器、频率选择寄存器,并且没有意外覆盖这些配置。2. **标志位状态**:读取中断标志寄存器,查看预期中断的标志位是否已被置位。3. **IRQ引脚电路**:确认开漏输出的IRQ引脚已通过电阻上拉到VCC,且未被其他电路短路。4. **中断服务程序**:确认在响应中断后,程序执行了读取中断标志寄存器的操作以清除标志,这是释放IRQ线的必要步骤。

关键摘要

- 引脚功能是基础:RTC-72421A的电源、晶振引脚保障基本运行,而CS、ALE、RD、WR构成了标准的并行总线接口,是与微处理器通信的物理通道。

- 时序逻辑是关键:必须严格遵循数据手册中CS、ALE、RD、WR等控制信号的时序参数,特别是建时间和保持时间,这是实现稳定数据读写的核心。

- 中断配置需细致:IRQ中断功能强大,但需要正确配置使能寄存器、频率寄存器,并在中断服务中妥善处理标志位的清除,才能可靠工作。

- 调试需系统化:遇到通信或中断问题时,应按照电源、时钟、控制信号时序、寄存器配置、外围电路的顺序进行系统性排查。

常见问题解答

RTC-72421A的CS引脚可以一直保持低电平吗?

在连续进行读写操作期间,CS引脚可以保持低电平。但如果长时间不操作,建议将CS拉高,使芯片进入低功耗待机模式以节省电能。需注意,从待机模式唤醒(CS拉低)到可以正常操作,需要一段短暂的稳定时间,设计时应予以考虑。

为什么按照时序操作,仍然无法读取RTC-72421A的时间寄存器?

除了检查基本时序,还需确认两点:第一,确保对时钟/日历寄存器的访问没有“锁定”。某些RTC在进行时间更新时会禁止读取,需要检查状态位。第二,确认读写的是正确的寄存器地址。RTC-72421A的内部RAM和时钟寄存器地址空间是分开的,访问时钟寄存器需要特定的命令序列或地址范围,请仔细核对数据手册的地址映射表。

RTC-72421A的IRQ中断输出不稳定,时有时无,可能是什么原因?

这通常与中断标志位的处理有关。首先,检查中断服务程序中是否清除了标志位。如果未清除,第一次中断后IRQ会一直保持有效,无法产生新的下降沿。其次,检查周期中断的周期设置是否过短,导致中断频率超过处理器响应速度,造成标志位堆积。最后,检查电源是否稳定,电压波动可能导致内部计时或逻辑错误。